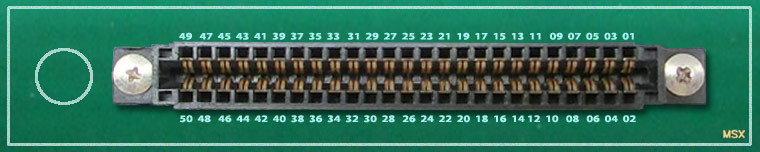

Port cartouche

Table des matières

Description des broches

| Broche | Nom | Type | Description |

| 01 | /CS1 | Sortie | Signal de sélection d'une ROM 16Ko de 4000H à 7FFFH. (Chip Select bank 1) Signal utilisé pour simplifier l'adressage. (lecture seule) |

| 03 | /CS12 | Sortie | Signal de sélection d'une ROM 32Ko de 4000H à BFFFH. (Chip Select bank 1 & 2) Signal utilisé pour simplifier l'adressage. (lecture seule) |

| 05 | RSV | N.C. | Réservé |

| 07 | /WAIT | Entrée | Signal d'attente pour le CPU. Utile seulement pour les circuits trop lents (mémoires, etc). Broche à relier sur une sortie collecteur ouvert. |

| 09 | /M1 | Sortie | Signal de la première étape du cycle d'une instruction (Fetch Cycle). |

| 11 | /IORQ | Sortie | Signal d'accès au port des E/S. |

| 13 | /WR | Sortie | Signal d'écriture d'une donnée. |

| 15 | /RESET | Sortie | Signal d'initialisation du système. |

| 17 | A09 | Sortie | Bit 9 d'adressage |

| 19 | A11 | Sortie | Bit 11 d'adressage |

| 21 | A07 | Sortie | Bit 7 d'adressage |

| 23 | A12 | Sortie | Bit 12 d'adressage |

| 25 | A14 | Sortie | Bit 14 d'adressage |

| 27 | A01 | Sortie | Bit 1 d'adressage. |

| 29 | A03 | Sortie | Bit 3 d'adressage. |

| 31 | A05 | Sortie | Bit 5 d'adressage. |

| 33 | D1 | E/S | Bit 1 du BUS de donnée. |

| 35 | D3 | E/S | Bit 3 du BUS de donnée. |

| 37 | D5 | E/S | Bit 5 du BUS de donnée. |

| 39 | D7 | E/S | Bit 7 du BUS de donnée. |

| 41 | GND | - | Masse |

| 43 | GND | - | Masse |

| 45 | +5V | - | Alimentation de 300mA max. par port cartouche. |

| 47 | +5V | - | Alimentation de 300mA max. par port cartouche. |

| 49 | SOUNDIN | Entrée | Signal sonore (-5dBm) |

| Broche | Nom | Type | Description |

| 02 | /CS2 | Sortie | Signal de sélection d'une ROM 16Ko de 8000H à BFFFH. (Chip Select bank 2) Signal utilisé pour simplifier l'adressage. (lecture seule) |

| 04 | /SLTSL | Sortie | Signal de sélection du SLOT. Chaque SLOT a son propre signal. |

| 06 | /RFSH | Sortie | Signal de rafraîchissement pour les DRAM. |

| 08 | /INT | Entrée | Signal de demande d'interruption. Broche à relier sur une sortie collecteur ouvert. |

| 10 | /BUSDIR | Entrée | Sens du bus de données. Utilisé que sur les MSX ayant un buffer sur les broches D0 ~ D7. |

| 12 | /MERQ | Sortie | Signal de demande d'accès à la mémoire provenant du CPU. Indique une opération de lecture/écriture d'une donnée en cours. |

| 14 | /RD | Sortie | Signal de lecture d'une donnée. |

| 16 | RSV | N.C. | Réservé. |

| 18 | A15 | Sortie | Bit 15 d'adressage |

| 20 | A10 | Sortie | Bit 10 d'adressage |

| 22 | A06 | Sortie | Bit 6 d'adressage |

| 24 | A08 | Sortie | Bit 8 d'adressage |

| 26 | A13 | Sortie | Bit 13 d'adressage |

| 28 | A00 | Sortie | Bit 0 d'adressage. |

| 30 | A02 | Sortie | Bit 2 d'adressage. |

| 32 | A04 | Sortie | Bit 4 d'adressage. |

| 34 | D0 | E/S | Bit 0 du BUS de donnée. |

| 36 | D2 | E/S | Bit 2 du BUS de donnée. |

| 38 | D4 | E/S | Bit 4 du BUS de donnée. |

| 40 | D6 | E/S | Bit 6 du BUS de donnée. |

| 42 | CLOCK | Sortie | Même signal d'horloge que le CPU à 3,579545Mhz mais avec un léger décalage. |

| 44 | SW1 | - | Reliée à SW2 pour indiquer qu'une cartouche est insérée. (Protection électrique) Cette broche doit être légèrement plus courte que les autres sur la cartouche. (Utilisée que sur les ports munis d'un switch. Permet l'insertion ou le retrait d'une cartouche le MSX allumé.) |

| 46 | SW2 | - | Reliée à SW1 pour indiquer qu'une cartouche est insérée. (Protection électrique) (Utilisée que sur les ports munis d'un switch. Permet l'insertion ou le retrait d'une cartouche le MSX allumé.) |

| 48 | +12V | - | Alimentation de 50mA max. pour tous les SLOT. Utile pour quelques cartouches comme l'FM-PAC, contrôleurs de disquette, etc. |

| 50 | -12V | - | Alimentation de 50mA max. pour tous les SLOT. Utile pour quelques cartouches comme l'FM-PAC, contrôleurs de disquette, etc. |

Notes :

- Le niveau des signaux sont compatibles avec les composants TTL (Transistor-Transistor Logic)

- Voir la description du Z80 pour plus infos sur les signaux.

Chronogrammes

Indique les timings maximum de bon fonctionnement.

Cycle M1 d'un SLOT primaire

Cycle M1 d'un SLOT secondaire

Cycle de la mémoire d'un SLOT primaire

Cycle de la mémoire d'un SLOT secondaire

Cycle des ports d'entrée/sortie d'un SLOT primaire

Cycle des ports d'entrée/sortie d'un SLOT secondaire

Nombre d'éléments (LS TTL) connectable (Fan-OUT et Fan-IN)

Fan-OUT et Fan-IN des données et du BUS d'adresse :

Fan-OUT et Fan-IN du signal de contrôle :

Dimensions

Côté cartouche :

Côté MSX :